Digital to Analog Converter

บทนำ

อุปกรณ์ทางไฟฟ้า/อิเล็กทรอนิกส์ โดยทั่วไปที่เป็นอะนาล็อก สามารถควบคุมการทำงานโดยการให้อินพุตเป็นระดับ แรงดันที่แตกต่างกัน ตัวอย่างเช่น มอเตอร์กระแส ตรง ซึ่งควบคุมความเร็วโดยเปลี่ยนระดับแรง ดัน (หรือ กระแส) ของขดลวดสนามเมื่อนำระบบดิจิตอล หรือไมโครคอนโทรลเลอร์ มาใช้ควบคุม อุปกรณ์ทางอะนาล็อก เหล่านี้ จึงต้องมีวงจรซึ่ง สามารถแปลงสัญญาณทางดิจิตอลเป็นระดับแรงดันต่อเนื่อง แบบอะนาล็อก ตั้งแต่ศูนย์โวลต์จนถึงระดับสูงสุดที่ กำหนดไว้ เรียกว่าวงจร Digital to Analog Converter (DAC)

คุณสมบัติ ของ Digital to Analog Converter

รูปที่ 1 แสดงถึงส่วนประกอบหลักของระบบ DAC โดย ทั่วไป ไมโครคอมพิวเตอร์จะมีเอาต์พุตเป็นค่าไบนารี วงจรแลทช์รับค่าไบนารี เข้ามาเพื่อส่งไปยัง DAC ในวงจรจะใช้แหล่งกำเนิดแรง ดันหรือ กระแสคงที่เพื่ออ้างอิงในการแปลงข้อมูล ไบนารี เป็นระดับกระแส ต่อมาจะมีวงจรแปลง จากกระแสเป็นระดับแรงดัน (current-to-voltage converter) ซึ่ง ปกติจะใช้ออปแอมป์ ท้ายสุด สัญญาณอะนาล็อกที่ได้จะผ่าน วงจร low-pass filter เพื่อกำจัดสัญญาณความถี่สูงที่ แฝงอยู่ในสัญญาณที่ถูกสร้างขึ้นมา

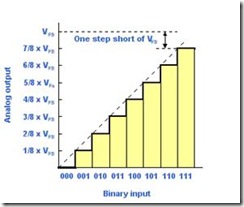

รูปที่ 2: Transfer Curve ในอุดมคติของ DAC 3 บิต

รูปที่ 2 เป็นกราฟแสดงถึงความสัมพันธ์ระหว่าง เอาต์พุตที่เป็นอะนาล็อกกับอินพุตที่เป็นดิจิตอลขนาด 3 บิตเรียกว่า transfer curve สังเกตว่าเมื่ออินพุตไบนารีเพิ่ม ขึ้น เอาต์พุตอะนาล็อกจะเพิ่ม ในลักษณะขั้นบันได ขนาดของแต่ละขั้นจะ หาได้จาก

stepsize = VFS/2n

เมื่อให้

VFS

คือระดับแรงดันเอาต์พุตสูงสุด

n

คือจำนวนบิตของอินพุต

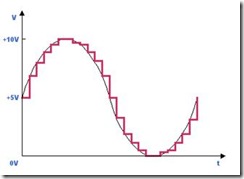

เนื่องจากเอาต์พุตของ DAC จะเพิ่มเป็นขั้นๆ รูปคลื่นสัญญาณ ที่ได้จาก DAC จึงมีลักษณะไม่เรียบ ดังตัวอย่าง ในรูปที่ 3 ซึ่งแสดงถึงสัญญาณไซน์ ที่สร้างจาก DAC

รูปที่ 3: คลื่นไซน์ที่สร้างจาก DAC

ถ้าเพิ่มจำนวนบิต ความละเอียดของ DAC จะเพิ่มขึ้น เช่น เมื่อ ใช้ DAC 12 บิต และ VFS = 5.0 V ความละเอียดคือ 5.0 V / 4096 = 1.22 mV ซึ่งจะ ละเอียดกว่า DAC 8 บิตถึง 16 เท่า

ความถูกต้องของ DAC ขึ้นอยู่กับหลายส่วน

1. Quantization error DAC บิต VFS = 5.0 V เอาต์พุตจะมีความละเอียด 19.53 mV ถ้าต้องการเอาต์พุต 4.00 V DAC จะให้เอาต์พุตได้ใกล้เคียง ที่สุดคือ 4.04 V (19.53 mV x 205) ผิดพลาด 4 mV โดยทั่วไปค่า ผิด พลาดจะเท่ากับ +/- 0.5 LSB (least significant bit) ตัวอย่างเช่น DAC 8 บิต ความผิดพลาดจะเป็น 1 ใน 512 หรือ +/- 0.195 %

2. Offset and gain errors เมื่ออินพุตไบนารี เท่ากับ 0 แต่เอาต์พุตของ DAC ไม่ เป็น 0 เรียก ว่า offset error และอาจเกิดร่วมกับ gain error ความผิดพลาดเหล่า นี้จะทำให้ tranfer curve ในรูปที่ 2 โค้งขึ้น หรือลง ขึ้นอยู่กับความไม่สม ดุลย์ภายใน DAC อย่างไรก็ ตาม offset error และ gain error จะแก้ได้โดยใช้ความต้าน ทานปรับค่าได้ต่อไว้ภายนอก

3. Nonlinearity คือค่าความคลาดเคลื่อนสูงสุดของ transfer curve เทียบกับเส้นตรงจากจุดศูนย์และจุดสูงสุด ซึ่งจะขึ้นอยู่กับความผิดพลาดของส่วนประกอบภาย ใน DAC ใน data sheet ของ DAC จะระบุเป็นเปอร์เซ็นต์เทียบกับค่าสูงสุด หรือ ระบุเป็นเศษส่วนของ LSB (โดยทั่วไปคือ +/- 0.5 LSB)

4. Settling time คือช่วงเวลานับแต่ให้อินพุตจนกระทั่ง DAC ให้ เอาต์พุต วัดเมื่อเอาต์พุตที่ได้ผิดพลาดจากค่าจริง น้อยกว่า 0.5 LSB ค่าเวลานี้อาจน้อยกว่า 100 ns สำหรับ DAC ความ เร็วสูง และอาจมากกว่า 100 us สำหรับ DAC ราคาถูก

วงจร Digital to Analog Converter

Summed Source DAC

รูปที่ 4: Summed Source DAC

เป็นวงจรอย่างง่ายในการแปลงสัญญาณดิจิตอลเป็น อะนาล็อก จาก รูปที่ 4 จะเห็นว่าเป็นวง จร Summing Amp มี ความต้านทานค่า 2R, 4R และ 8R เพื่อทำให้ กระแสที่ผ่านความต้านทานแต่ละตัวมีค่า ลดลงเป็น 2 เท่า ความต้านทานตัวล่างสุด (2R) จะ เป็น MSB ส่วนตัวบนสุดจะเป็น LSB

ข้อเสียของการใช้วงจรลักษณะนี้ ในทางปฏิบัติ ค่าความต้านทานที่ต่างกันเป็น 2 เท่า คือ 2R, 4R, 8R, … จะ ไม่สามารถหาได้ง่าย จึงมีการปรับปรุงเป็น วงจร R-2R

Switched Voltage R-2R DAC

รูปที่ 5: Swiched Voltage R-2R DAC

รูปที่ 5 เป็น DAC 3 บิต ใช้ออปแอมป์และความต้านทาน เพียง 2 ค่าคือ R และ 2R สังเกตว่าอินพุตดิจิตอลจะมาจากสวิตช์ทั้ง 3 ซึ่ง อาจต่อกับกราวด์ (ลอจิก 0) หรือต่อกับ VREF (ลอจิก 1) ตัวอย่าง นี้อินพุตเป็น 001

พิจารณากระแส I เมื่อผ่านจุด A จะถูกแบ่งเป็นสองส่วน เท่าๆ กัน เหลือ I/2 เมื่อผ่านจุด B และ C จะถูกแบ่งอีกครั้ง เหลือ I/4 และ I/8 ตามลำดับ ดังนั้นกระแสที่ป้อนให้กับออปแอมป์จะ เหลือ I/8 เมื่อพิจารณาที่สวิตช์ตัวอื่นๆ ก็จะมีลักษณะคล้ายกัน ดังนั้นกระแสที่ผ่านออปแอมป์เมื่อ ปิดสวิตช์อื่นนับจากซ้าย มาขวา จะมีขนาด I/8, I/4 และ I/2 ตามลำดับ สวิตช์ซ้ายสุด จะเป็น LSB ส่วนขวาสุดจะ เป็น MSB

Switched Current R-2R DAC

รูปที่ 6: Swiched Current R-2R DAC

วงจรนี้เปลี่ยนจากการใช้แรงดันอ้างอิง (VREF) มาเป็นกระแสอ้างอิง (IR) กระแสที่ ผ่านสวิตช์แต่ละตัวจากขวามาซ้ายจะเป็น IR/2, IR/4 และ IR/8 ตามลำดับ วงจร ลักษณะนี้จะมีความเร็วสูงกว่าวงจร Switched Voltage เนื่องจาก คาปาซิแตนซ์ที่รอยต่อ (junction capacitance) ของความต้าน ทานแต่ละตัวจะไม่ถูกชาร์จและดิสชาร์จเหมือนวง จร Switched Voltage

Switched Pole DAC

รูปที่ 7: Swiched Pole DAC

จะมีการใช้ความต้านทานต่ออนุกรมกัน หลายตัว เนื่องจากวงจรนี้ต้องการความต้าน ทานค่าเท่าๆ กัน ดังนั้นจึงเป็นที่นิยมสำหรับ ผู้ผลิต Integrated Circuit สังเกตว่าจะมีความต้านทานที่ ปลายทั้งสองของอนุกรมเพื่อปรับ offset ของเอาต์พุต