ตัวเลื่อนข้อมูล (SHIFT REGISTER)

ตัวเลื่อน ข้อมูลจัดเป็นการนำ FLIP FLOP ไปใช้งานได้ อย่างหนึ่ง การเลื่อนข้อมูลจะมีลักษณะแตกต่างกันดังนี้

1. เข้าขนานออกขนาน (Parallel In Parallel Out หรือ PIPO)

2. เข้าขนาน ออก อนุกรม (Parallel In Serial Out หรือ PISO)

3. การเข้าอนุกรม ออก ขนาน (Serial In Parallel Out หรือ SIPO)

4. เข้าอนุกรม ออก อนุกรม (Seraill In Serail Out หรือ SISO)

5. การรับส่งข้อมูลในระบบ คอมพิวเตอร์

ตัวเลื่อน ข้อมูลดังกล่าวแล้วข้างต้นใช้โครงสร้างจาก FLIP FLOP ซึ่งแบ่งออก เป็น R-S FLIP FLOP , D FLIP FLOP หรือ J-K FLIP FLOP ก็ได้

INPUT

PR CLR CLK D

OUTPUT

Q nQ

0 1 X X

1 0 X X

0 0 X X

1 1 X

1 1 0

1 1 0 X

1 0

0 1

1* 1*

1 0

0 1

Q0 nQ0

1* ไม่ stable

รูป 1 โครงสร้างและตารางเอาท์พุทของ 7474 ซึ่งเป็น FLIP-FLOP ชนิด D

nQ = Qbar = Q complement , nQ0 = Q0bar = Q0 complement

จากรูป 1 ขอให้สังเกตว่า เพียงแต่ให้ PRESET เป็น "0" จะทำให้ OUTPUT 0 = "1" และเมื่อ CLR = "0" จะทำให้ Q เป็น "0" แต่ทั้ง PRESET และ CLEAR (CLR) จะต้องมีลอจิกตรงกันข้าม

1* ไม่ stable

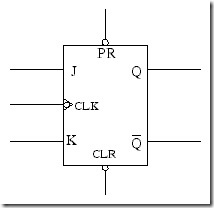

รูป 2 J-K FLIPFLOP 7476

INPUT

PR CLR J K CLK

OUTPUT

Q nQ

0 1 X X X

1 0 X X X

0 0 X X X

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

1 1 X X 1

1 1 X X 0

1 0

0 1

1* 1*

Q0 nQ0

0 1

1 0

toggle

Q0 nQ0

Q0 nQ0

nQ = Qbar = Q complement , nQ0 = Q0bar = Q0 complement

โดยโครงสร้างและลอจิกของ JK FLIPFLOP สามารถจะนำมาดัดแปลงให้มีคุณสมบัติเทียบเท่ากับ D FLIPFLOP ได้ดังแสดงในรูป 3

7476 JK-FLIPFLOP 7473 D-FLIPFLOP

รูป 3 แสดงการดัดแปลง JK FLIPFLOP ให้มีคุณสมบัติแบบเดียวกับ D FLIPFLOP

1. ตัวเลื่อนข้อมูล แบบเข้าขนานและ ออกขนาน

ตัวเลื่อนข้อมูลในลักษณะนี้ จะนำมาใช้เป็นตัวจดบันทึก หรือคงค่า (latch) ข้อมูล เพื่อให้เห็นภาพของการใช้งานชัดเจน ขอให้ดูตัวอย่างดังต่อไปนี้

1.1 ตัวบันทึกข้อมูลแบบ 2 บิท

จากคุณสมบัติดังตารางในรูป 1 เรานำฟลิปฟลอปดังกล่าวแล้วมาสร้างเป็นตัวรับข้อมูลแบบ 2 บิท จะได้ดังรูป 4

รูป 4 ตัวรับข้อมูลแบบ 2 บิท

รูป 5 แสดง ความสัมพันธ์ระหว่าง DATA CLOCK

และ DATA OUTPUT

ในรูป 5 เป็นความสัมพันธ์ระหว่างสัญญาณเอาท์พุท กับ สัญญาณ DATA ที่สัญญาณ CLOCK แสดงจังหวัดเวลาต่าง ๆ กัน โดยการเปลี่ยนแปลงจะเกิดขึ้นทั้งขอบขาขึ้นของสัญญาณพัลส์

จากรูป 4 เป็นตัวอย่างของตัวบันทึกข้อมูลแบบ 2 บิท หากจะให้จำนวนบิทมากขึ้น ก็เพียงแต่เพิ่มจำนวนฟลิปฟลอป แล้วใช้สัญญาณ CLOCK ร่วมกัน

1.2 ตัวบันทึกข้อมูล แบบ 8 บิท

จากหลักการในรูป 4 สามารถดัดแปลงให้รับข้อมูลแบบ 8 บิทได้โดยใช้ D-FLIPFLOP จำนวน 8 ตัวมาต่อขนานกันแล้ว ใช้สัญญาณ CLOCKร่วมกัน จะได้ตัวรับข้อมูลแบบ 8 บิท

แม้จะใช้ฟลิปฟลอปจำนวนหลาย ตัวต่อเป็นตัวบันทึกข้อมูลแบบ 8 บิทก็ตาม แต่ก็มีไอซีชนิด 8 บิท LATCH สำเร็จรูปให้ใช้หลายตัว เช่น 74LS373 หรือ 74LS374 ซึ่งใช้เป็นตัวบันทึกข้อมูลสำหรับไอซีไมโครโปรเซสเซอร์

2. ตัวเลื่อนข้อมูล แบบเข้าขนานออกอนุกรม การส่งข้อมูลให้กับตัวเลื่อนชนิดนี้ ทำได้โดยการส่งข้อมูลให้ตัวเลื่อนแบบขนาน และรับข้อมูลจากตัวเลื่อนแบบอนุกรม

รูป 7 ตัวเลื่อนข้อมูล ชนิดรับส่งข้อมูลเข้าแบบขนาน และส่งข้อมูลแบบอนุกรม โดยใช้ฟลิปฟลอป ชนิด J - K

จากรูป 7 ข้อมูลที่ต้องการจะ LOAD เข้ามาแบบขนานจะต้องป้อนเข้ามารอไว้ที่ D2 D1 D0 เมื่อได้สัญญาณ LOAD เป็น "1" จะได้รับการ LOAD เป็น "0" จะยังคงสภาพ "0" อยู่เหมือนเดิม

ลำดับขั้นตอนในการใช้ PISO ตามโครงสร้างนี้ จะต้องทำตามลำดับขั้นดังนี้

1. CLEAR วงจร โดยส่งสัญญาณ CLEAR เป็น ลอจิก "0" ชั่วขณะ (ปกติ ขานี้จะต้องเป็น "1" เพื่อให้ JK FLIPFLOP ทำงาน)

2. LOAD ค่าที่ต้องการ

3. SHIFT ข้อมูลตามกระบวนการ

ต่อไปนี้เป็นตัวอย่างการใช้ตัวเลื่อนข้อมูลแบบรับส่ง ข้อมูลแบบขนานแล้วส่งออกแบบอนุกรม โดยใช้ ฟลิปฟลอป ชนิด D

รูป 8 ตัวรับข้อมูลแบบขนาน 4 บิท และส่งออกอนุกรม เมื่อให้สัญญาณเคลียร์ เอาท์พุทของทุกตัวมาเป็นลอจิก "0" เมื่อ ให้สัญญาณ Preset ตัว ที่มีข้อมูลเข้ามาเป็น "1" จะมีเอาท์พุท Q เป็นลอจิก 1 ด้วย ให้ดูรูป 9 ประกอบ

รูป 9 แสดงการเลื่อนของข้อมูล 1001 ออกไปทางขวา Q0 โดยบิทที่มีค่าต่ำสุด (LSB) จะ เลื่อนออกไปก่อน

การส่งข้อมูลในลักษณะนี้ตัวข้อมูลจะเลื่อนออกไปทางสาย สัญญาณเพียงเส้นเดียว โดยบิทที่มีค่าต่ำสุด (Least Significant Bit หรือ LSB) จะ เลื่อนออกไปหลังสุด จำนวนบิทของข้อมูลจะกำหนดจำนวนทดของ FlipFlop และจำนวนสัญญาณนาฬิกาที่ต้องใช้ ในการเลื่อนข้อมูล

3. ตัวเลื่อนข้อมูล แบบส่งเข้าแบบอนุกรม และส่งออกแบบขนาน

มีโครงสร้างดังแสดงในรูป 10

รูป 10 โครงสร้างของตัวเลื่อนข้อมูลแบบ เข้าอนุกรมและออกแบบขนาน ใช้ฟลิปฟลอปชนิด J-K

ตัวเลื่อนข้อมูลแบบ SIPO สามารถนำเอาท์พุท มาใช้ได้ใน 2 ลักษณะ คือ

1. นำ เอาท์พุทขนานมาใช้ คือ OUTPUT QA, QB, QC และ QD

2. นำ เอาท์พุทอนุกรมมาใช้ คือ จาก QA มาใช้ การนำเอาท์พุทขนานมาใช้ จะต้องอาศัยการเลื่อน 4 จังหวะ จึงจะได้ข้อมูลมา ครบถ้วน ส่วนข้อมูลอนุกรมจะได้ครบก็ต่อเมื่อต้องอาศัยการเลื่อน 8 จังหวะ

ปกติตัวเลื่อนแบบ SISO จะนำมาใช้เมื่อ ต้องการหน่วงเวลาสัญญาณเท่านั้น

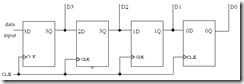

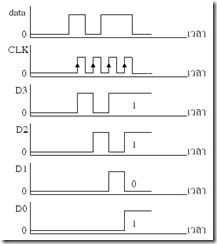

ต่อไปนี้เป็นตัวอย่างการใช้ฟลิปฟลอปชนิด D ในการเลื่อนข้อมูล แบบรับเข้าอนุกรม และส่งออกแบบขนาน

รูป 11 การนำ D FLIPFLOP มาจัดวงจรเป็นรับเข้าแบบอนุกรม และส่งออกแบบขนาน

รูป 12 หลังจากมีสัญญาณ CLOCK เข้ามาครบ 4 ลูก DATA ที่ส่งเข้ามาในจังหวะที่สัมพันธ์กับสัญญาณ CLOCK จะปรากฎออกมาที่ ขา D3 D2 D1 และ D0

การรับข้อมูลแบบอนุกรมในลักษณะนี้สัญญาณ CLOCK ของฝ่ายรับจะ ต้องมีคาบเวลาเท่ากับสัญญาณ CLOCK ของฝ่ายหลัง (แต่ไม่ จำเป็ฯต้องเป็นสัญญาณเดียวกัน) ข้อมูลที่รับได้จึงจะเป็นข้อมูลที่ถูกต้อง

4. ตัวเลื่อนข้อมูล ชนิดรับเข้าแบบอนกรมและส่งออกแบบอนุกรม

ในการส่งข้อมูลแบบอนุกรมและตัวรับแบบอนุ กร มนี้ไม่มีใช้ในการรับส่งข้อมูลทั่วไป แต่ใช้เพื่อหน่วงเวลาของข้อมูล หากต้องการ หน่วงเวลาของข้อมูลไป 1 ช่วงสัญญาณนาฬิกาก็ได้ ฟลิปฟลอปชนิด D จำนวน 1 ภาค และเพิ่มขึ้นทุกจำนวน 1 ภาค ต่อการหน่วง ไป 1 จังหวะของสัญญาณนาฬิกา อย่างไรก็ตามจำนวนบิทของข้อมูลที่ส่งต่อหน่วยเวลาจะต้องเท่ากับความถี่ของ สัญญาณนาฬิกาที่ให้กับ ฟลิปฟลอปชนิดD

รูป 13 แสดงการหน่วงเวลาของข้อมูลโดย การสงเข้าแบบ อนุกรมและส่งออกแบบอนุกรม

รูป 14 แสดงการหน่วงเวลาของข้อมูลโดย ใช้ D FLIPFLOP จำนวน 2 ภาค เพื่อสร้างเป็นตัวรับแบบอนุกรม และส่งออกแบบอนุกรม

แบบฝึกหัด

3. ให้ เขียนวงจร PISO และ SIPO โดยใช้ D FLIP-FLOP ของเบอร์ 7474

4. ให้ รวบรวมไอซี SHIFT REGITER ตามคู่มือว่ามีเบอร์อะไรบ้าง

5. ให้ หาตัวอย่างการใช้งานของ SHIFT REGISTER ทุก ประเภท จากวารสาร หรือเอกสาร พร้อมทั้งระบุเอกสารอ้างอิง

การทดลอง

6. ให้ ใช้ IC 74175 ออกแบบวงจร SHIFT REGISTER พร้อมทั้งทดสอบคุณสมบัติ เป็นผังเวลา

§ SHIFT REGISTER แบบ PIPO

§ SHIFT REGISTER แบบ SIPO และ SISO

7. ใช้ ไอซี 74164 ส่งเอาท์พุทไปขับ LED ด้วยข้อ มูฐล 11000101

§ ให้ เขียนวงจรให้เต็มรูปแบบ

§ ให้ ส่งเอาท์พุทไปขับ LED ตามข้อมูลที่กำหนด

§ ให้ มีสัญญาณเคลียร์เอาท์พุทให้เป็น 0

8. ไอ ซี 74166 ออกแบบมาเพื่อเป็นรีจิสเตอร์ชนิดใด และสามารถใช้งานเป็นรีจิสเตอร์ใดได้บ้าง

5. การรับ ส่งข้อมูลในระบบคอมพิวเตอร์

9. การรับส่งแบบขนาน

การรับส่งแบบขนานนี้ จะต้องใช้สายสัญญาณต่อขนานกันหลายเส้น

รูป 16 แสดงแผนผังของการรับ ส่งข้อมูลแบบขนาน

เช่น สายข้อมูลอย่างน้อย 8 เส้น สายสัญญาณ clock สายควบคุม สายตอบรับ และสาย common การรับส่งข้อมูล ในลักษณะนี้ จะกระทำเฉพาะระยะทางสั้น ๆ ไม่เกิน 100 ฟุต หากสายส่งยาวเกินไปการรับ ส่งจะผิดพลาด เนื่องจาก สัญญาณเพี้ยนเพราะความต้านทานและความจุของของสายสัญญาณ และที่สำคัญก็คือสายส่งมีราคาแพง

ตัวอย่างการรับส่งแบบนี้ได้แก่การรับส่งข้อมูลระหว่าง คอมพิวเตอร์กับเครื่องพิมพ์ และเครื่องอ่านบันทึกจานแม่เหล็กเป็นต้น

10. การรับส่งข้อมูลแบบอนุกรม

การรับส่งสัญญาณในลักษณะนี้ ในตัวส่งจะต้องมีตัวแปลงสัญญาณจากขนานเป็นอนุกรม และในตัวรับ จะต้องมีตัวแปลง สัญญาณจากอนุกรมเป็นขนานโดยมีหลักการดังนี้

รูป 17 แสดงหลักการพื้นฐาน ของการรับส่งข้อมูลแบบอนุกรม

ในการรับส่งข้อมูลแบบขนานนี้จะต้องตกลงกันทั้งฝ่ายรับและ ฝ่ายส่งว่าจะใช้อัตราเร็วในการรับส่งเท่าใดซึ่งจะต้อง ตกลงกันสองฝ่ายข้อมูลที่ได้รับจึงจะถูกต้อง